taper. Conventional machining of the taper may be impractical, but other techniques can be devised. It is, however, emphasized that the transition described here was not intended for production but for a specific measurement program [16].

#### ACKNOWLEDGMENT

The authors wish to express their appreciation to W. Wibbelink and J. Brand for the manufacture of the trial transition.

#### REFERENCES

- [1] T. Yoneyama and S. Nishida, "Nonradiative dielectric waveguide for millimeter-wave integrated circuits," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-29, pp. 1188-1192, Nov. 1981.

- [2] T. Yoneyama, S. Nishida, and M. Yamaguchi, "Bends in nonradiative dielectric waveguide," in *1982 IEEE MTT-S Dig.*, pp. 300-301.

- [3] T. Yoneyama, M. Yamaguchi, and S. Nishida, "Bends in nonradiative dielectric waveguide," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-30, pp. 2146-2150, Dec. 1982.

- [4] T. Yoneyama, N. Tozawa, and S. Nishida, "Coupling characteristics of nonradiative dielectric waveguides," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-31, pp. 648-654, Aug. 1983.

- [5] T. Yoneyama and S. Nishida, "Nonradiative dielectric waveguide circuit components," *Int. J. Infrared and Millimeter Waves*, vol. 4, no. 3, 1983.

- [6] T. Yoneyama, S. Fujita, and S. Nishida, "Insulated nonradiative dielectric waveguide for millimeter-wave integrated circuits," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-31, pp. 1002-1008, Dec. 1983.

- [7] J. A. G. Malherbe, T. N. Trinh, and R. Mittra, "Transition from metal to dielectric waveguide," *Microwave J.*, vol. 23, no. 11, pp. 71-74, Nov. 1980.

- [8] R. F. Harrington, *Time-Harmonic Electromagnetic Fields*. New York: McGraw-Hill, 1961.

- [9] R. W. Klopfenstein, "A transmission line taper of improved design," *Proc. IRE*, vol. 44, pp. 31-35, Jan 1956.

- [10] R. P. Hecken, "A near-optimum matching section without discontinuities," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-20, pp. 734-739, Nov. 1972.

- [11] R. E. Collin, *Foundations for Microwave Engineering*. New York: McGraw-Hill, 1966.

- [12] R. E. Collin, *Field Theory of Guided Waves*. New York: McGraw-Hill, 1960.

- [13] P. H. Vartanian, W. P. Ayres, and A. I. Helgesson, "Propagation in dielectric slab loaded rectangular guide," *IRE Trans. Microwave Theory Tech.*, vol. MTT-6, pp. 215-222, Apr. 1958.

- [14] W. Schlosser and H-G. Unger, "Partially filled waveguides and surface waveguides of rectangular cross section," in *Advances in Microwaves*, vol. 1, L. Young, Ed. New York: Academic Press, 1966, pp. 319-387.

- [15] F. E. Gardiol, "Higher-order modes in dielectrically loaded rectangular waveguides," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-16, pp. 919-924, Nov. 1968.

- [16] J. A. G. Malherbe *et al.*, "The design of a slot array in nonradiating dielectric waveguide—Part II: Experiment," *IEEE Trans. Antennas Propagat.*, vol. AP-32, pp. 1341-1344, Dec. 1984.

- [17] F. A. Benson and F. J. Tischer, "Some guiding structures for millimeter waves," *Proc. Inst. Elec. Eng.*, vol. 131, pt. A, no. 7, pp. 429-449, Sept. 1984.

- [18] A. A. Oliner, "Historical perspectives on microwave field theory," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-32, pp. 1022-1045, Sept. 1984.

- [19] J. A. G. Malherbe, laboratory notebook, Univ. of Illinois, May 8, 1979.

## A Low-Noise GaAs Monolithic Broad-Band Amplifier Using a Drain Current Saving Technique

K. OSAFUNE, N. KATO, T. SUGETA, AND Y. YAMAO

**Abstract**—A low-noise and low-power GaAs monolithic broad-band amplifier is proposed and has been developed, which has a new cascade connection with a large gate-width input FET and the other circuits in such

Manuscript received August 25, 1984; revised January 15, 1985.

K. OsaFune, N. Kato, and T. Sugeta are with Atsugi Electrical Communication Laboratory, Nippon Telegraph and Telephone Public Corporation, Atsugi, Japan.

Y. Yamao is with Yokosuka Electrical Communication Laboratory, Nippon Telegraph and Telephone Public Corporation, Yokosuka, Japan.

a way that the output stage current flows through the input FET. The fabricated amplifier operates on +5-V single supply voltage, and provides a 3.3-dB noise figure, less than 180-mW power dissipation, and a 10-MHz-2.0-GHz bandwidth with 16-dB gain.

#### I. INTRODUCTION

Recent advances in GaAs IC technology make it possible to develop GaAs monolithic broad-band amplifiers for mobile radio applications. For these amplifiers, both a low dc power dissipation and a low noise figure are required. From a practical point of view, single-power supply operation and good input/output matching are desirable. To meet these needs, low-noise, low power-dissipation GaAs monolithic broad-band amplifiers were developed [1]-[3]. They achieved a low noise figure and good input/output matching by using *RC* parallel feedback, and also achieved low power dissipation by using inductive loads (choke coils). Although inductive loads are effective in reducing amplifier power dissipation, choke coil sizes are almost 10 times as large as IC chips below the S-band.

In this short paper, we propose a new circuit construction which enables both power saving and low-noise operation in the monolithic GaAs amplifier for VHF-UHF mobile radio systems. Design considerations and performance characteristics of this amplifier are described as follows.

#### II. CIRCUIT DESIGN

In order to construct a low-noise amplifier, it is desirable to increase the input-stage FET transconductance  $g_m$ . Therefore, the input-stage FET must have a wide gate width to afford high  $g_m$ . To make input matching, a resistor negative feedback circuit is advantageous from the view point of low-noise characteristics. Furthermore, if the amplifier open-loop gain is high, the feedback resistor can be increased, and the noise generated from the feedback resistor can be suppressed. For increasing the open-loop gain, multistage construction is effective [2]. But dc drain current also increases as the number of the stages increases. If we can get high gain without a drain current increase, both a low noise figure and low power dissipation are possible.

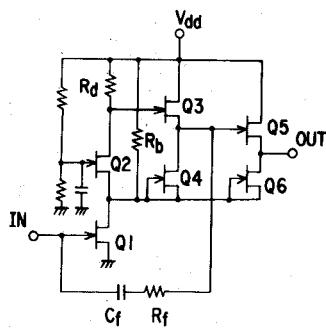

For this purpose, a new circuit construction amplifier (shown in Fig. 1) has been developed. This amplifier consists of three stages; the input stage ( $Q1, Q2$ ) and two source follower stages ( $Q3, Q4$  and  $Q5, Q6$ ). The input stage owns a wide-gate input FET  $Q1$  and a relatively high-impedance resistor load  $R_d$  to obtain both a low noise figure and high gain. The amplifier open-loop gain is mainly determined by this stage. The two source follower stages do not amplify signal voltages, but they do lower the amplifier output impedance to  $50 \Omega$ . The small input capacitance of the intermediate source follower FET  $Q3$  makes it possible to increase the resistor load  $R_d$  without decreasing the amplifier bandwidth; thus, the open-loop gain increases as well. The output matching is performed by determining the transconductance of the output FET  $Q5$  equal to  $20 \text{ mS}$  ( $=1/50 \Omega$ ). A negative feedback circuit ( $R_f, C_f$ ) is used for input matching with little influence on the noise figure. The gate-grounded FET  $Q2$  is used to make the input FET drain voltage constant and yields bias voltages of current source FET's  $Q4$  and  $Q6$ .

In this construction, the bias currents of two source follower stages pass through  $Q1$ . Therefore, the amplifier's total drain current is equal to that of the input FET  $Q1$ . Due to the adoption of this multistage cascade construction, high gain and a low noise figure are attained without an increase in current.

Fig. 1. Schematic diagram for a newly developed GaAs monolithic amplifier.

$R_f$ : Feedback resistor.

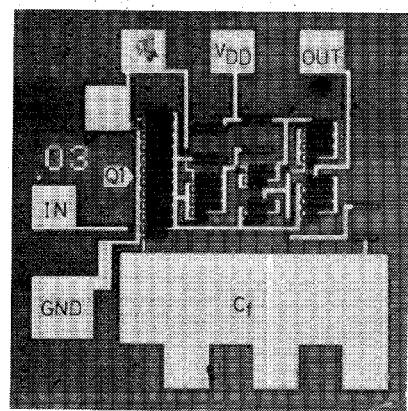

Fig. 2. Microphotograph of the fabricated amplifier.

TABLE I

DESIGN PARAMETERS OF THE AMPLIFIER

$W_g$ : GATE-WIDTH.

| 540 $\mu\text{m}$ |       |              |

|-------------------|-------|--------------|

| $W_g$             | Q1    | 170          |

|                   | Q2    | 85           |

|                   | Q3    | 85           |

|                   | Q4    | 170          |

|                   | Q5    | 170          |

|                   | Q6    | 170          |

|                   |       |              |

|                   | $R_d$ | 600 $\Omega$ |

|                   | $R_b$ | 530          |

|                   | $R_f$ | 1200         |

|                   | $C_f$ | 17 pF        |

The amplifiers' design parameters are shown in Table I. Gate length and threshold voltage for the FET's used are  $0.7 \mu\text{m}$  and  $-1 \text{ V}$ , respectively. The intermediate source follower FET  $Q_3$  gate width is determined by circuit simulations for the amplifier bandwidth to be as broad as possible.

Scattering parameters and the noise figure are calculated by circuit simulation programs ASTAP and SPICE with the FET model described in [4] and [5].

### III. FABRICATION

The amplifiers were fabricated by the self-aligned implantation for  $n^+$ -layer technology (SAINT) [6] process. Active layers for the FET's and the low sheet-resistive layers ( $500 \Omega/\text{square}$ ) for resistors were formed by two ion implantations into a 2-in LEC wafer. The capacitors are MIM-type, where the dielectric material is PCVD-SiN. Details of the other processes are described in [7].

A microphotograph of the fabricated amplifier chip is shown in Fig. 2. The gate finger width for the FET's and the space between the electrode for resistors were both  $50 \mu\text{m}$ . Chip size was  $0.8 \times 0.8 \text{ mm}^2$ .

### IV. PERFORMANCE

The amplifiers were mounted on  $50\Omega$  coplanar test fixtures and their characteristics were measured by an automatic network analyzer (HP-8545A) and an automatic noise-figure meter (AIL-75).

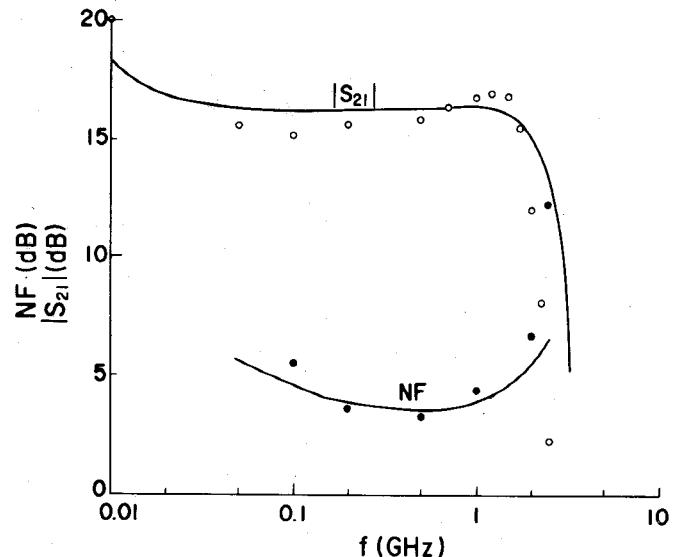

Frequency dependences for transducer gain  $S_{21}$  and noise figure NF for the amplifier are shown in Fig. 3. The amplifier had a 16-dB flat gain and a 2-GHz, 3-dB bandwidth under a power dissipation of  $180 \text{ mW}$  ( $V_{dd} = +5 \text{ V}$ ). The calculated frequency dependences for transducer gain  $S_{21}$  are shown by the solid line

Fig. 3. The frequency dependences of the transducer gain  $S_{21}$  and noise figure for the amplifier. Points show measured values. Solid lines indicate the calculated frequency dependences of  $S_{21}$  and NF.

in Fig. 3. In this computer simulation, the average value of transconductance ( $110 \text{ mS/mm}$  at  $V_{ds} = 1.5 \text{ V}$  and  $V_{gs} = 0 \text{ V}$ ) for the fabricated FET was used. Drain conductance and parasitic capacitances were considered to obtain the best fitting. The amplifier had a 3.3-dB noise figure NF at approximately 1 GHz. Fig. 3 also shows the computed frequency dependences for the noise figure using the modified SPICE simulation program for a GaAs FET, assuming that  $P = 2$ , where  $P$  is the well-known factor in the expression for the drain current noise defined by  $i_{dn} = 4kT\Delta f g_m P$ .

The amplifier developed here is briefly compared to recently reported GaAs monolithic amplifiers. The noise figure of the amplifier is much lower than that of a common gate-type monolithic amplifier [8]. The power dissipation of the amplifier is sufficiently lower than that of common source-type amplifiers with resistive feedback [9]–[11], though the noise figure is slightly higher than that of those amplifiers.

### V. CONCLUSION

A low-noise, low power-dissipation GaAs monolithic broadband amplifier has been developed for VHF–UHF mobile radio systems. The amplifier operates with a single power supply, requires no external choke coils, provides a 3.3-dB noise figure

with less than 180-mW dc power dissipation, and has a 10-MHz-2.0-GHz bandwidth with 16-dB gain. It has been concluded that the new circuit construction is effective for low-noise, low power-dissipation GaAs monolithic amplifiers. This amplifier is capable for use in mobile radio systems.

#### ACKNOWLEDGMENT

The authors wish to thank the members of the processing group for the fabrication, and also Dr. M. Ohmori for his constant encouragement.

#### REFERENCES

- [1] K. Honjo, T. Sugiura, T. Tsuji, and T. Ozawa, "Low-noise, low-power-dissipation GaAs monolithic broadband amplifiers," in *Proc. 1982 GaAs IC Symp.*, pp. 87-90.

- [2] M. Nishiuma, S. Katsu, S. Nambu, M. Hagio, and G. Kano, "A 2.2 dB NF 30-1700 MHz feedback amplifier," in *ISSCC Dig. Tech. Papers*, Feb. 1983, pp. 194-195.

- [3] J. Tajima, Y. Yamao, T. Sugita, and M. Hirayama, "GaAs monolithic low-power amplifiers with RC parallel feedback," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-32, pp. 542-544, May 1984.

- [4] T. Takada, M. Togashi, and T. Hirota, "GaAs MESFET circuit simulation model," in *Papers Techn. Group, TGSSD83-124*, IECE Japan, pp. 9-16.

- [5] T. Takada, K. Yokoyama, M. Ida, and T. Sudo, "A MESFET variable-capacitance model for GaAs integrated circuit simulation," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-30, pp. 719-724, May 1982.

- [6] K. Yamasaki, K. Asai, T. Mizutani, and K. Kurumada, "Self-align implantation for N<sup>+</sup>-layer technology (SAINT) for high-speed GaAs IC's," *Electron. Lett.*, vol. 18, no. 3, pp. 119-121, Feb. 1982.

- [7] M. Hirayama, M. Ino, Y. Matsuoka, and M. Suzuki, "A GaAs 4kb SRAM with direct coupled FET logic," in *ISSCC Dig. Tech. Papers*, Feb. 1984, pp. 46-47.

- [8] D. B. Estrich, "A monolithic wide-band GaAs IC amplifier," *IEEE J. Solid-State Circuits*, vol. SC-17, pp. 1166-1173, Dec. 1982.

- [9] J. A. Archer, H. P. Weidlich, E. Pettenpaul, F. A. Petz, and J. Huber, "A GaAs monolithic low-noise broad-band amplifier," *IEEE J. Solid-State Circuits*, vol. SC-16, pp. 648-652, Dec. 1981.

- [10] M. Nishiuma, S. Nambu, M. Hagio, and G. Kano, "A GaAs monolithic low-noise wideband amplifier," presented at the 1981 Int. Symp. GaAs Related Compounds, 1981.

- [11] W. C. Peterson, A. K. Gupta, and D. R. Decker, "A monolithic GaAs dc to 2 GHz feedback amplifier," in *IEEE 1982 Microwave Millimeter-wave Monolithic Circuits Symp. Dig. Tech. Papers*, June 18, 1982, pp. 20-22.

#### Polygonal Coaxial Line with Round Center Conductor

WEIGAN LIN

**Abstract**—The complex potential function  $W = A(\ln z + C_N z^N)$  generates a zero-potential line approximating a regular polygon of  $N$  sides very closely, except in the nearly field-free region. By means of this function we work out the characteristic impedance, the power-carrying capacity, and the attenuation constant of the polygonal line of  $N$  sides with a round inner coaxial conductor in a closed form of elementary functions with good accuracy compared to more complex solutions.

Results for  $N = 3$  are believed to be nearly as good as those available in the literature.

#### I. INTRODUCTION

Considerable work has been done on transmission lines in which the two conductors are not members of the same orthogonal cylindrical coordinate system. These are difficult electrostatic

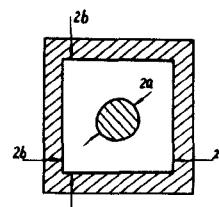

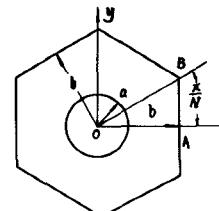

Fig. 1. TEM coaxial line with round inner and square outer conductor.

Fig. 2. TEM coaxial line with polygonal outer conductor of  $N$  sides and round inner conductor.

problems, one of which is the well-known charged sphere in a cylinder [1]. Riblet solved the characteristic impedance of a TEM coaxial line with a round inner and square outer conductor (shown in Fig. 1) and also of the related transmission line of a square inner and round outer conductor by means of a well-known transformation, work that first appeared in 1935 [2]. Subsequent work appeared in 1982 on this same problem [3], [7]. The purpose of this paper is to investigate the characteristics of the coaxial line with a round inner conductor of radius  $a$  and a polygonal outer conductor of  $N$  sides with an inscribed circle of radius  $b$ , as shown in Fig. 2. In comparison with the existing data, all our results are in closed forms, in elementary functions, and have accuracy nearly as good as data available in the literature, but the simplicity in the  $Z_0$  formula surpasses all of them except for  $N = 4$ . The forms of our results allow us to calculate the power-carrying capacity and the attenuation constant of the line.

#### II. THE METHOD

We generalize Schelkunoff's work on the TEM transmission line with a round inner conductor and square outer conductor [4] by the following complex potential function:

$$W = U + jV = A \left[ \ln \frac{z}{R} + C_N \left( \frac{z}{R} \right)^N \right] \quad (1a)$$

with

$$U = A \left[ \ln \frac{\rho}{R} + C_N \left( \frac{\rho}{R} \right)^N \cos N\varphi \right] \quad (1b)$$

$$V = A \left[ \varphi + C_N \left( \frac{\rho}{R} \right)^N \sin N\varphi \right] \quad (1c)$$

where  $(\rho, \varphi)$  are the polar coordinates, and  $A$ ,  $R$ , and  $C_N$  are constants to be determined to fit the boundary conditions of the coaxial line of Fig. 2. If  $U$  and  $V$  are, respectively, the potential and the flux function, it follows that the charge per unit length  $Q$  of this coaxial line is

$$Q = \epsilon [V] = 2\pi\epsilon A. \quad (2)$$

Now  $C_N$  is nonzero, so the zero-potential line is determined by the following equation from (1b):

$$-C_N \cos N\varphi = \left( \frac{\rho}{R} \right)^N \ln \frac{\rho}{R}. \quad (3)$$

Manuscript received January 25, 1984; revised January 14, 1985.

The author is with Chengdu Institute of Radio Engineering, Chengdu, Sichuan, 610054, People's Republic of China.